# Elliptic Curve Cryptography for Constrained Devices

Dissertation submitted to the Faculty of Electrical Engineering and Information Technology at the Ruhr-University Bochum

> for the Degree of Doktor-Ingenieur

> > by

Sandeep S. Kumar Bochum, Germany, June 2006

Author contact information: kumar@crypto.rub.de http://www.sandeepkumar.org

Thesis Advisor: Prof. Christof Paar Thesis Reader: Prof. Ingrid Verbauwhede to my parents for their love and support

# Abstract

There is a re-emerging demand for low-end devices such as 8-bit processors, driven by needs for pervasive applications like sensor networks and RF-ID tags. Security in pervasive applications, however, has been a major concern for their widespread acceptance. Public-key cryptosystems (PKC) like RSA and DSA generally involve computation-intensive arithmetic operations with operand sizes of 1024 - 2048 bits, making them impractical on such constrained devices.

*Elliptic Curve Cryptography* (ECC) which has emerged as a viable alternative is a favored public-key cryptosystem for embedded systems due to its small key size, smaller operand length, and comparably low arithmetic requirements. However, implementing full-size, standardized ECC on 8-bit processors is still a major challenge and normally considered to be impracticable for small devices which are constrained in memory and computational power.

The thesis at hand is a step towards showing the practicability of PKC and in particular ECC on constrained devices. We leverage the flexibility that ECC provides with the different choices for parameters and algorithms at different hierarchies of the implementation. First a secure key exchange using PKC on a low-end wireless device with the computational power of a widely used 8-bit 8051 processor is presented. An *Elliptic Curve Diffie-Hellman* (ECDH) protocol is implemented over 131-bit Optimal Extension Field (OEF) purely in software. A secure end-to-end connection in an acceptable time of 3 seconds is shown to be possible on such constrained devices without requiring a cryptographic coprocessor.

We also investigate the potential of software/hardware co-design for architectural enhancements including instruction set extensions for low-level arithmetic used in ECC, most notably to speed-up multiplication in the finite fields. We show that a standard compliant 163-bit point multiplication can be computed in 0.113 sec on an 8-bit AVR micro-controller running at 4 Mhz (a typical representative for a low-cost pervasive processor) with minimal additional hardware extensions. Our design not only accelerates the computation by a factor of more than 30 compared to a software-only solution, it also reduces the code-size and data-RAM. Two new custom instructions for the MIPS 32-bit processor architecture are also proposed to accelerate the reduction modulo a pseudo Mersenne prime. We also show that the efficiency of multiplication in an OEF can be improved by a modified multiply and accumulate unit with a wider accumulator. The proposed architectural enhancements achieve a speed-up factor of 1.8 on the MIPS processor. In addition, different architectural enhancements and optimal digit-size choices for the Least Significant Digit (LSD) multiplier for binary fields are presented. The two different architectures, the Double Accumulator Multiplier (DAM) and N-Accumulator Multiplier (NAM) are both faster compared to traditional LSD multipliers.

Later, an area/time efficient ECC processor architecture (for the OEFs of size 169, 289 and 361 bits) which performs all finite field arithmetic operations in the discrete Fourier domain is described. We show that a small optimized implementation of ECC processor with 24k equivalent gates on a 0.35um CMOS process can be realized for 169-bit curve using the novel multiplier design. Finally we also present a highly area optimized ASIC implementation of the ECC processor for various standard compliant binary curves ranging from 133 - 193 bits. An area between 10k and 18k gates on a 0.35um CMOS process is possible for the different curves which makes the design very attractive for enabling ECC in constrained devices.

# Kurzdarstellung

Aufgrund der allgegenwärtigen Präsenz von eingebetteten Systemen, z.B. basierend auf Sensornetzwerken und RF-ID-Tag, ist wieder eine zunehmende Nachfrage nach kostengünstigen Geräten, wie z.B. 8-Bit Mikroprozessoren, zu beobachten. Dabei stellt die kryptographische Sicherheit dieser Geräte eine größe Hürde für ihre breite Akzeptanz dar. Asymmetrische Kryptosysteme (engl. public-key cryptosystems, PKC) wie RSA und DSA sind nicht für den Einsatz auf solchen beschränkten, eingebetteten Geräten geeignet, weil sie im Allgemeinen für arithmetische Operationen Langzahlen (1024-2048 Bit Operanden) verwenden.

Die Elliptische Kurven Kryptographie (engl. Elliptic Curve Cryptography, ECC) hat sich als geeignete Alternative für eingebettete Systeme herausgestellt, weil sie mit kleinen Schlüssellängen, kleineren Operanden und vergleichsweise geringen arithmetischen Anforderungen auskommt. Die Implementierung eines standardisierten ECC Algorithmus auf 8-Bit Prozessoren stellt indes immer noch eine große Herausforderung dar, die als nicht praktikabel für rechen- und speicherbeschränkte Geräte angesehen wird.

In dieser Dissertation wird die Umsetzbarkeit von asymmetrischen Verfahren, insbesondere der Elliptische Kurven Kryptographie, auf Geräten mit beschränkten Resourcen behandelt. Die Elliptische Kurven Kryptographie ermöglicht ein großes Maß an Flexibilität aufgrund möglicher Freiheitsgrade bzgl. der Wahl verschiedenener Parameter und Algorithmen, welche in dieser Arbeit diskutiert und effizient implementiert werden. So wird zuerst gezeigt, dass es möglich ist, einen sicheren Schlüsselaustausch basierend auf ECC auf einem kostengünstigen, für drahtlose Anwendungen ausgelegten Prozessor (vergleichbar mit dem dem weit verbreiteten 8-Bit 8051 Mikroprozessor) zu implementieren. Diese gänzlich auf Software basierende Implementierung des Diffie-Hellman Protokolls mit Elliptischen Kurven (Elliptic Curve Diffie-Hellman, ECDH) führt arithmetische Berechnungen in einem optimalen 131-Bit Erweiterungskörper (optimal extension field, OEF) durch. Eine kryptografisch sichere Verbindung zwischen zwei Endteilnehmern wird auf einem solchen Gerät ohne kryptographischen Co-Prozessor innerhalb von drei Sekunden hergestellt.

Desweiteren untersuchen wir die Möglichkeiten von Software/Hardware Co-Design Ansätzen um mittels Architekturmodifikationen, z.B. Befehlssatzerweiterungen (Instruction Set Extensions, ISE) für körperarithmetische Basisoperationen wie sie bei ECC zum Einsatz kommen, die Performanz zu steigern. Es wird gezeigt, dass eine standardisierte 163-Bit Punkt-Multiplikation mit minimalen zusätzlichen HardwareKosten auf einem 8-Bit AVR Mikro-Controller (ein typischer, kostengünstiger Prozessor), der mit 4 MHz getaktet ist, in 0,113 Sekunden ausgeführt werden kann. Dieses Design bringt im Vergleich zu einer rein Software-basierten Implementierung einen Geschwindigkeitsgewinn um mehr als das 30-fache, während die Größe des Quelltext verringert und weniger Arbeitspeicher verbraucht wird. Zusätzlich werden zwei neue Befehle für den MIPS 32-Bit Prozessor vorgeschlagen, die Reduktionen modulo Pseudo-Mersenne Primzahlen beschleunigen. Desweiteren wird gezeigt, dass für Multiplikationen in einem OEF ein vergrösserter Akkumulator in der ALU von Vorteil ist. Die vorgestellte Architektur führt zu einem Geschwindigkeitszuwachs um 180

Darüber hinaus werden architektonische Verbesserungen sowie optimale Parameter für Least Significant Digit (LSD) Multiplizierer für Binärkörper vorgestellt. Die architektonischen Verbesserungen basieren auf einem Double Accumulator Multiplier (DAM) und N-Accumulator Multiplier (NAM), welche beide klassische LSD Multiplizierer bzgl. der Geschwindigkeit übertreffen.

Im Anschluß wird eine effiziente ECC-Prozessorarchitektur (für 169-bit, 289-bit und 361-bit OEF) vorgestellt, die alle arithmetischen Operationen im Frequenzbereich durchführt. So wird eine optimierte 169-Bit OEF ECC Implementierung mit 24K Logikgattern für einen 0.35um CMOS Prozess präsentiert.

Schließlich wird eine flächenoptimierte ECC ASIC Implementierung für Binärköper mit standardisierte 133 bis 193 Bits vorgestellt. Es wird gezeigt, dass lediglich 10K bis 18K Logikgatter für eine 0.35um CMOS Implementierung benötigt werden. Daher eignet sich diese ECC Architektur insbesondere für kostengünstige Implementierungen, wie sie z.B. in drahtlosen Netzwerken zum Einsatz kommen.

# Preface

## ॐ भूर्भुवः स्वः तत्सवितुर्वरेण्यं। भर्गो देवस्य धीमहि। धियो यो नः प्रचोदयात्॥

This thesis describes the research that I conducted during the three and half years I worked as a researcher at the Ruhr-University Bochum. I hope that the results of this work are a step towards practical acceptance of *Elliptic Curve Cryptography* (ECC) in constrained devices among researchers and in the industry.

The work, I present in this thesis, would not have been possible without the support of several people. First of all, I would like to thank my advisor, Prof. Christof Paar, who gave me the opportunity to come to Germany and work under him. His advice and expertise in the field have been indispensable throughout my research. I would also like to thank Prof. Paar for his valuable friendship and camaraderie that has developed while working together with him. I would also like to thank my thesis committee, especially Prof. Ingrid Verbauwhede for the valuable suggestions, comments and advise that they gave me.

I would also like to thank my colleagues who have now become good friends over time. A special thanks to Kathy and Jorge Guajardo for their invaluable help in adjusting to Germany, being wonderful friends, and constant support during my stay here. To Thomas Wollinger for the interesting discussions on and about Deutsch we had every morning, thereby improving my vocabulary and not to forget the work we did together on digit multipliers. Andre Weimerskirch for being understanding and helpful during our industry projects. To Jan Pelzl and Kai Schramm for initiating me to the true German culture, for all those wonderful parties and fun we had at Dresden. Andy Rupp for all the help I could get just across the door. Kerstin Lemke-Rust for all the work we did together and managing the student projects. Thanks to Tim Güneysu for checking through the last minute additions to my thesis. Thomas Eisenbath, Marcus Heitmann, Timo Kasper, Axel Poschmann, Marko Wolf, and all the students for the wonderful atmosphere at COSY. Not to forget, is the most important person at COSY, our team assistant Irmgard Khn who helped with the terrible bureaucracy. Thanks also to the computer administrators, Marcel Selhorst, Christian Röpke and Horst Edelmann for being patient with all my demands.

There are also several other people whom I would like to thank for the contributions to my work. Thanks to Johann Großschädl for the work done together on the extensions for MIPS and Selcuk Baktir for the work on the frequency domain ECC. Thanks to Marco Girimondo for the patience and hard work involved in getting the Chipcon model ready for the SunNetwork 2003. Ho Won Kim for the fruitful discussions on VHDL and cryptographic hardware designs. I would also like to thank Holger Bock for the internship opportunity at Infineon Graz.

Last, but not least, I would like to thank my parents and my brother for their support, and bearing with the fact that we could not meet more often. Thanks to my cousin for her wonderful mails.

To all of you, thank you very much!!

Sandeep

Be the change you want to see in the world. - Mabatma Gandhi

# **Table of Contents**

| A        | Abstract |          |                                                                 |     |  |

|----------|----------|----------|-----------------------------------------------------------------|-----|--|

| K        | urzda    | arstellı | ıng                                                             | v   |  |

| P        | refac    | е        |                                                                 | vii |  |

| 1        | Intr     | oducti   | on                                                              | 1   |  |

|          | 1.1      | Securi   | ty Requirements and Techniques                                  | 2   |  |

|          |          | 1.1.1    | Public-Key Cryptography                                         | 3   |  |

|          |          | 1.1.2    | Elliptic Curve Cryptography (ECC)                               | 5   |  |

|          | 1.2      | Thesis   | Outline                                                         | 6   |  |

| <b>2</b> | Mat      | themat   | ical Background                                                 | 9   |  |

|          | 2.1      | Introd   | uction to Elliptic Curves                                       | 9   |  |

|          | 2.2      | Ellipti  | c Curve Parameter Selection                                     | 10  |  |

|          | 2.3      | Ellipti  | c Curve Arithmetic over $\mathbb{F}_p$                          | 11  |  |

|          |          | 2.3.1    | Field Arithmetic over $\mathbb{F}_p$                            | 13  |  |

|          | 2.4      | Ellipti  | c Curve Arithmetic over $\mathbb{F}_{2^m}$                      | 17  |  |

|          |          | 2.4.1    | Field Arithmetic over $\mathbb{F}_{2^m}$                        | 18  |  |

|          | 2.5      | Ellipti  | c Curve Arithmetic over $\mathbb{F}_{p^m}$                      | 22  |  |

|          |          | 2.5.1    | Field Arithmetic over Optimal Extension Fields (OEF) $\ldots$ . | 23  |  |

|          | 2.6      | Ellipti  | c Curve Point Multiplication                                    | 27  |  |

|          |          | 2.6.1    | Binary Method                                                   | 28  |  |

|          |          | 2.6.2    | Non-Adjacent Form (NAF) Method                                  | 28  |  |

|          |          | 2.6.3    | Windowing Methods                                               | 28  |  |

|          |          | 2.6.4    | Montgomery Method                                               | 29  |  |

|          | 2.7      | Ellipti  | c Curve Key Exchange and Signature Protocols                    | 30  |  |

|          |          | 2.7.1    | Elliptic Curve Diffie-Hellman Key Exchange                      | 30  |  |

|   |                  | 2.7.2 Elliptic Curve Digital Signature Algorithm                                           | 31              |

|---|------------------|--------------------------------------------------------------------------------------------|-----------------|

| 3 | Soft             | tware Design: ECDH Key Exchange on an 8-bit Processor                                      | <b>32</b>       |

|   | 3.1              | Motivation and Outline                                                                     | 32              |

|   | 3.2              | Related Work                                                                               | 33              |

|   | 3.3              | The Chipcon Architecture                                                                   | 33              |

|   | 3.4              | Elliptic Curve Parameter Selection                                                         | 33              |

|   | 3.5              | Implementation aspects on the Chipcon processor                                            | 34              |

|   |                  | 3.5.1 Field Arithmetic                                                                     | 34              |

|   |                  | 3.5.2 Point Arithmetic                                                                     | 36              |

|   | 3.6              | Communication Protocol                                                                     | 37              |

|   |                  | 3.6.1 Key Establishment Phase                                                              | 38              |

|   |                  | 3.6.2 Normal Mode                                                                          | 39              |

|   | 3.7              | Demonstration Application                                                                  | 39              |

|   | 3.8              | Summary                                                                                    | 41              |

| 4 | Har              | dwone /Software Co. designs, Extensions for on 8 bit Dresser                               | 49              |

| 4 | <b>па</b><br>4.1 | dware/Software Co-design: Extensions for an 8-bit Processor         Motivation and Outline | <b>42</b><br>42 |

|   | 4.1              | Related Work                                                                               | 42              |

|   | 4.3              | The FPSLIC Architecture                                                                    | 43              |

|   | 4.4              | Implementation aspects on the AVR processor                                                | 43<br>44        |

|   | 7.7              | 4.4.1 Field Arithmetic                                                                     | 45              |

|   |                  | 4.4.2 Point Arithmetic                                                                     | 46              |

|   | 4.5              | Proposed Instruction Set Extensions                                                        | 46              |

|   | 1.0              | 4.5.1 8-by-8 Bit-Parallel Multiplier                                                       | 49              |

|   |                  | 4.5.2 163-by-163 Bit-Serial Multiplier                                                     | 49              |

|   |                  | 4.5.3 163-by-163 Digit Serial Multiplier                                                   | 50              |

|   |                  | 4.5.4 A Flexible Multiplier                                                                | 51              |

|   | 4.6              | Summary                                                                                    | 52              |

|   |                  |                                                                                            |                 |

| 5 |                  | rdware/Software Co-design: Extensions for a 32-bit Processor                               | 56              |

|   | 5.1              | Motivation and Outline                                                                     | 56              |

|   | 5.2              | Related work                                                                               | 57              |

|   | 5.3              | The MIPS32 architecture                                                                    | 58              |

|   | 5.4              | Implementation aspects on the MIPS32 processor                                             | 59              |

|   | 5.5              | Proposed extensions to MIPS32                                                              | 61              |

|   |                  | 5.5.1 Multiply/accumulate unit with a 72-bit accumulator                                   | 62              |

|   |              | 5.5.2 Custom instructions                                                   | 63         |

|---|--------------|-----------------------------------------------------------------------------|------------|

|   |              | 5.5.3 Implementation details and performance evaluation                     | 63         |

|   | 5.6          | Summary                                                                     | 66         |

| 6 | Har          | rdware Design: Optimal Digit Multipliers for $\mathbb{F}_{2^m}$             | 67         |

|   | 6.1          | Motivation and Outline                                                      | 67         |

|   | 6.2          | Background on Digit-Serial Multipliers                                      | 68         |

|   | 6.3          | Architecture Options for LSD                                                | 69         |

|   |              | 6.3.1 Single Accumulator Multiplier (SAM)                                   | 70         |

|   |              | 6.3.2 Double Accumulator Multiplier (DAM)                                   | 74         |

|   |              | 6.3.3 N-Accumulator Multiplier (NAM)                                        | 78         |

|   | 6.4          | Evaluation of the Multiplier Options                                        | 79         |

|   |              | 6.4.1 Evaluation of the SAM                                                 | 80         |

|   |              | 6.4.2 Evaluation of all multiplier options                                  | 82         |

|   | 6.5          | Summary                                                                     | 83         |

| 7 | Har          | rdware Design: ECC in the Frequency Domain                                  | 86         |

|   | 7.1          | Motivation and Outline                                                      | 86         |

|   | 7.2          | Mathematical Background                                                     | 87         |

|   |              | 7.2.1 Number Theoretic Transform (NTT)                                      | 87         |

|   |              | 7.2.2 Convolution Theorem and Polynomial Multiplication in the              |            |

|   |              | Frequency Domain                                                            | 88         |

|   | 7.3          | Modular Multiplication in the Frequency Domain                              | 89         |

|   |              | 7.3.1 Mathematical Notation                                                 | 90         |

|   |              | 7.3.2 DFT Modular Multiplication Algorithm                                  | 90         |

|   |              | 7.3.3 Optimization                                                          | 91         |

|   | 7.4          | Implementation of an ECC Processor Utilizing                                |            |

|   |              | DFT Modular Multiplication                                                  | 94         |

|   |              | 7.4.1 Base Field Arithmetic                                                 | 94         |

|   |              | 7.4.2 Extension Field Multiplication                                        | 95         |

|   |              |                                                                             |            |

|   |              | 7.4.3 Point Arithmetic                                                      | 99         |

|   | 7.5          |                                                                             | 99<br>100  |

|   | $7.5 \\ 7.6$ | 7.4.3       Point Arithmetic          Performance Analysis          Summary |            |

| 8 | 7.6          | Performance Analysis                                                        | 100<br>102 |

| 8 | 7.6          | Performance Analysis                                                        | 100        |

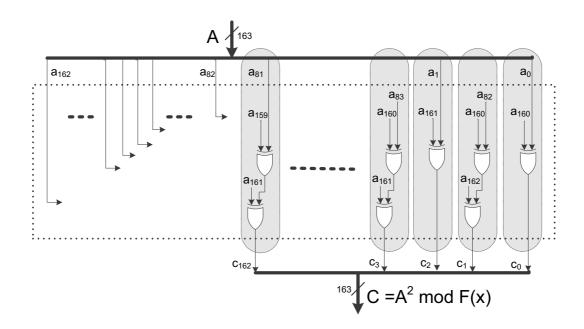

|    |       | 8.2.1   | Squaring                                                                                                                                             | 108 |

|----|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |       | 8.2.2   | Inversion                                                                                                                                            | 108 |

|    |       | 8.2.3   | Point multiplication                                                                                                                                 | 110 |

|    | 8.3   | Impler  | mentation Aspects                                                                                                                                    | 113 |

|    |       | 8.3.1   | $\mathbb{F}_{2^m}$ Adder Unit                                                                                                                        | 113 |

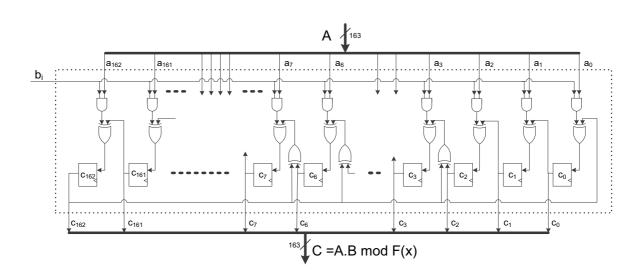

|    |       | 8.3.2   | $\mathbb{F}_{2^m}$ Multiplier Unit                                                                                                                   | 113 |

|    |       | 8.3.3   | $\mathbb{F}_{2^m}$ Squarer Unit                                                                                                                      | 115 |

|    |       | 8.3.4   | ECC Processor design                                                                                                                                 | 116 |

|    | 8.4   | Perfor  | mance Analysis                                                                                                                                       | 118 |

|    | 8.5   | Summ    | ary                                                                                                                                                  | 120 |

| 9  | Disc  | cussion | 1                                                                                                                                                    | 123 |

|    | 9.1   | Conclu  | usions                                                                                                                                               | 123 |

|    | 9.2   | Future  | $e \text{ Research } \ldots $ | 124 |

| Bi | bliog | graphy  |                                                                                                                                                      | 126 |

# **List of Figures**

| 1.1  | Public-key encryption protocol                                                                                                        | 4  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | $y^2 = x^3 + a \cdot x + b$ over the reals                                                                                            | 10 |

| 2.2  | Multiply-and-accumulate strategy $(m = 4)$                                                                                            | 24 |

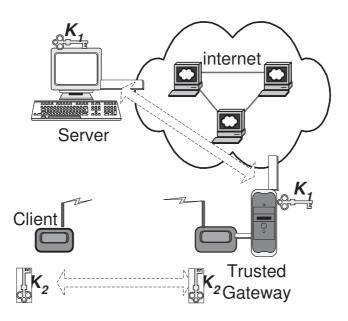

| 3.1  | Network security based on a trusted gateway.                                                                                          | 38 |

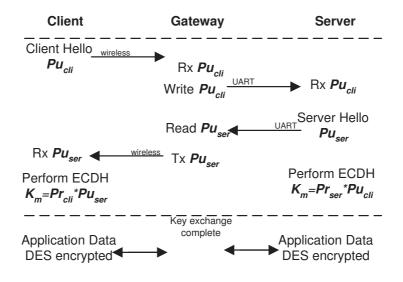

| 3.2  | Key exchange protocol                                                                                                                 | 39 |

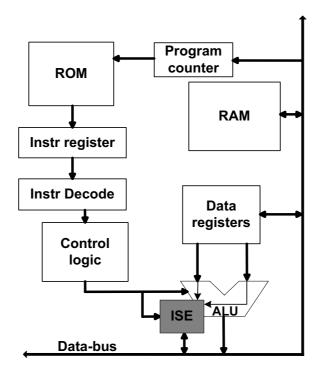

| 4.1  | Processor Core with Extension                                                                                                         | 47 |

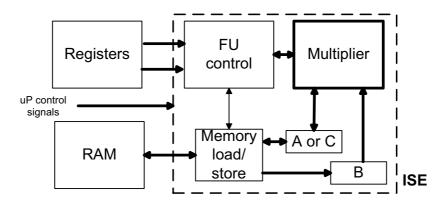

| 4.2  | ISE Interface and Structure                                                                                                           | 48 |

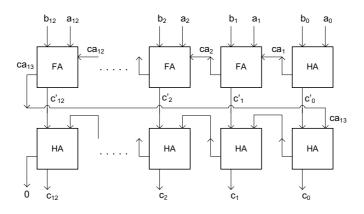

| 4.3  | Bit-Serial LSB Multiplier                                                                                                             | 50 |

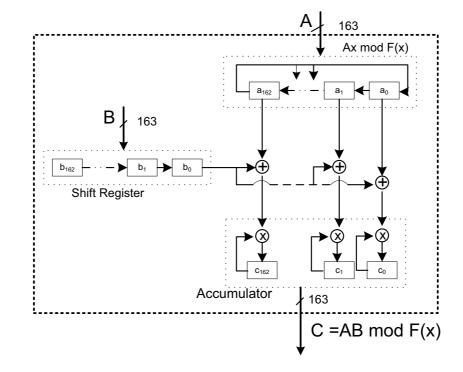

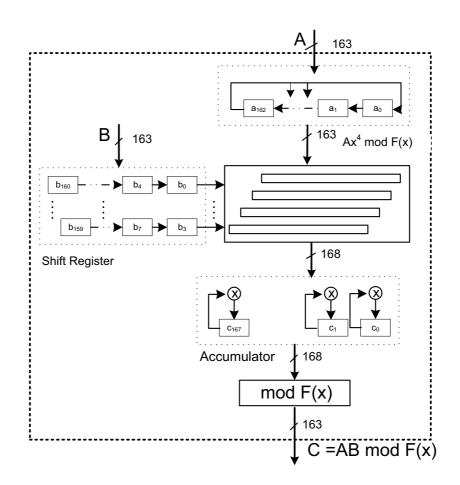

| 4.4  | Digit-4 Serial LSD Multiplier                                                                                                         | 51 |

| 4.5  | Bit-serial reduction circuit                                                                                                          | 52 |

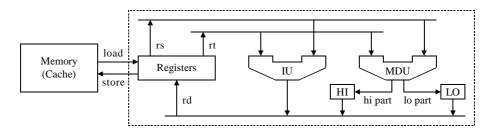

| 5.1  | $4\mathrm{Km}$ data<br>path with integer unit (IU) and multiply/divide unit (MDU)                                                     | 58 |

| 5.2  | Calculation of a column sum and subfield reduction                                                                                    | 64 |

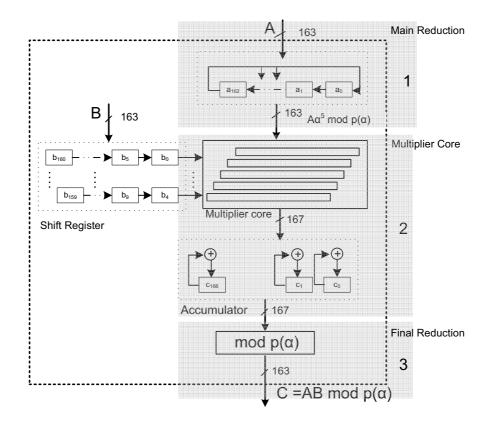

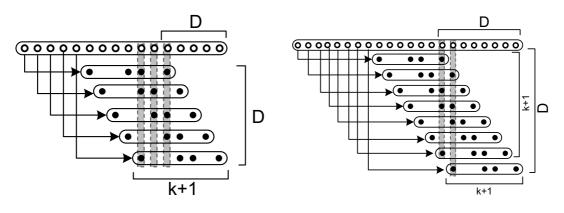

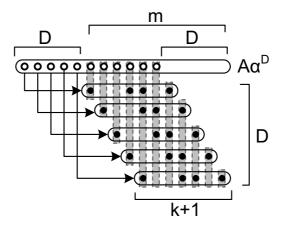

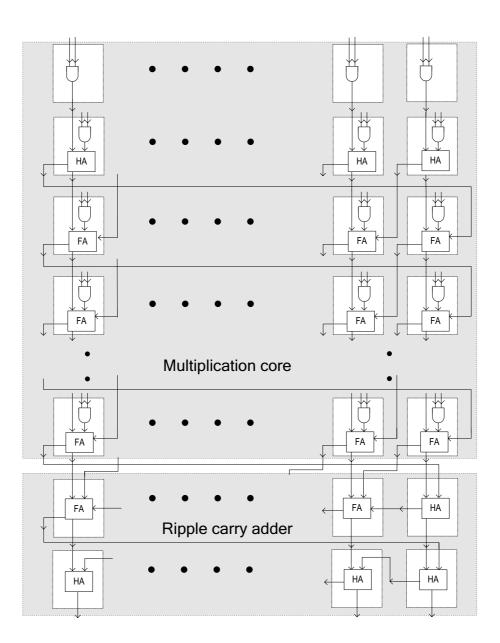

| 6.1  | LSD-Single Accumulator Multiplier Architecture $(D=5)$ for $\mathbb{F}_{2^{163}}$                                                     | 70 |

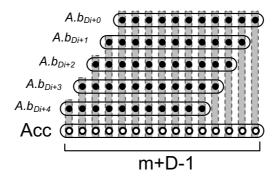

| 6.2  | SAM multiplier core for $D = 5 \dots \dots$ | 71 |

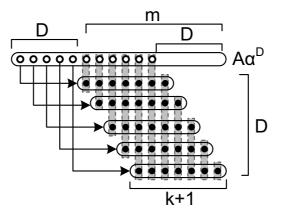

| 6.3  | SAM main reduction circuit for $D = 5$                                                                                                | 72 |

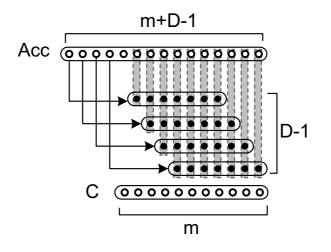

| 6.4  | SAM final reduction circuit for $D = 5 \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                         | 73 |

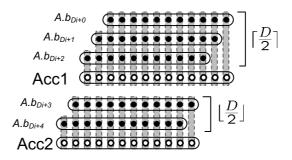

| 6.5  | DAM multiplier core for $D = 5$                                                                                                       | 74 |

| 6.6  | Overlap case                                                                                                                          | 75 |

| 6.7  | Underlap case                                                                                                                         | 75 |

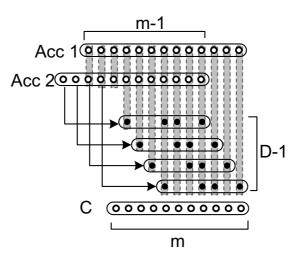

| 6.8  | DAM main reduction circuit for $D = 5$                                                                                                | 77 |

| 6.9  | DAM final reduction circuit for $D = 5$                                                                                               | 78 |

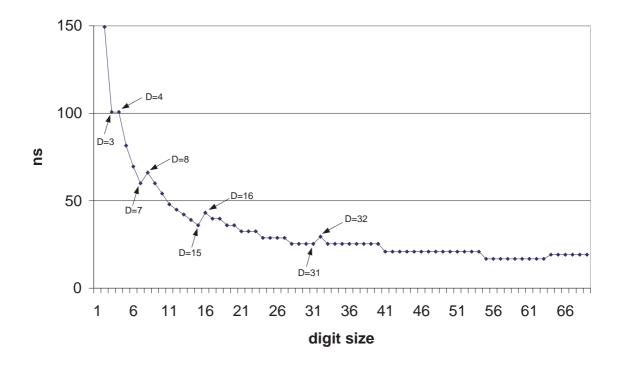

| 6.10 | Time to complete one multiplication of the single accumulator multiplier                                                              | 81 |

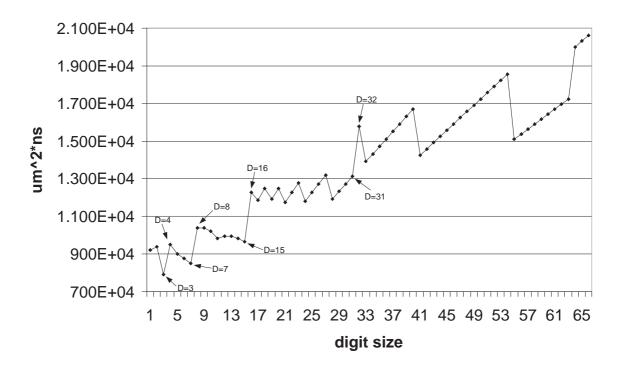

| 6.11 | Area-Time Product of the single accumulator multiplier                                                                                | 82 |

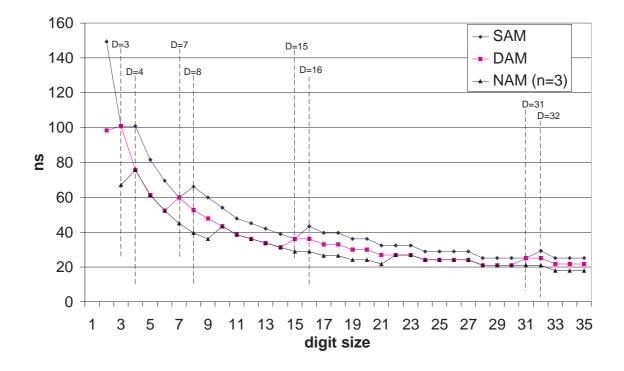

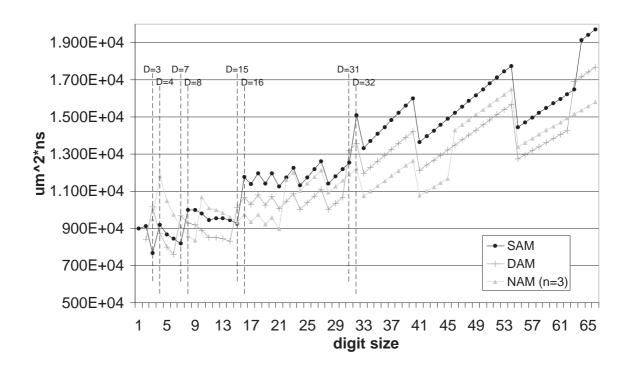

| 6.12 | 2 Time to complete one multiplication of all the different multiplier im-                          |     |  |  |

|------|----------------------------------------------------------------------------------------------------|-----|--|--|

|      | plementations                                                                                      | 83  |  |  |

| 6.13 | Area-Time Product of the different multiplier implementations                                      | 84  |  |  |

| 7.1  | Base Field Addition Architecture                                                                   | 94  |  |  |

| 7.2  | Base Field Multiplication with Interleaved Reduction                                               | 96  |  |  |

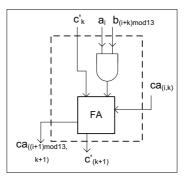

| 7.3  | Processing Cell for the Base Field Multiplier Core                                                 | 97  |  |  |

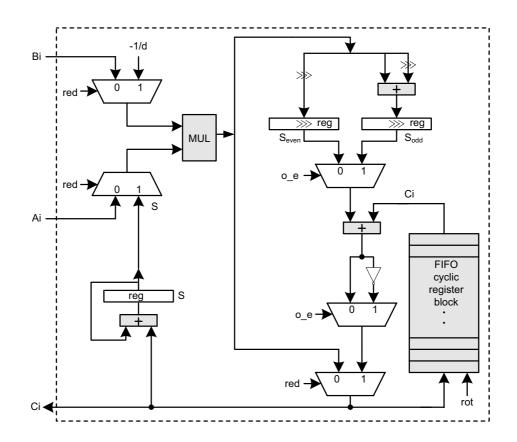

| 7.4  | DFT Montgomery Multiplication architecture                                                         | 99  |  |  |

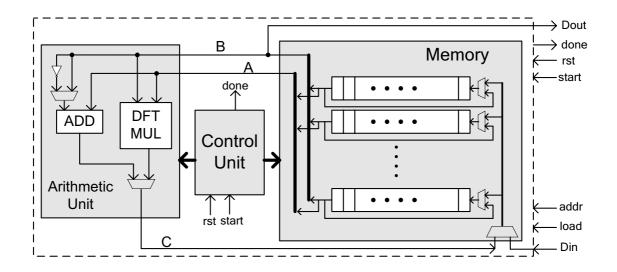

| 7.5  | Top Level ECC Processor Architecture                                                               | 101 |  |  |

| 8.1  | $\mathbb{F}_{2^{163}}$ Most Significant Bit-serial (MSB) Multiplier circuit $\ldots \ldots \ldots$ | 115 |  |  |

| 8.2  | $\mathbb{F}_{2^{163}}$ squaring circuit                                                            | 116 |  |  |

| 8.3  | Area optimized $\mathbb{F}_{2^n}$ ECC processor                                                    | 117 |  |  |

# **List of Tables**

| 1.1 | Key length for public–key and symmetric–key cryptography                                                                                             | 5   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Operation counts for point addition and doubling on $y^2 = x^3 - 3x + b$ .<br>A = affine, P = standard projective, J = Jacobin, I = field inversion, |     |

| 2.2 | Operation counts for point addition and doubling on $y^2 + xy = x^3 +$                                                                               | 13  |

|     | $ax^2 + b$ . $M =$ field multiplication, $D =$ field division [34] $\dots \dots \dots$                                                               | 18  |

| 3.1 | Field arithmetic performance on Chipcon (@3.68 Mhz) $\ldots \ldots \ldots$                                                                           | 36  |

| 3.2 | ECC point arithmetic performance on Chipcon (@3.68 Mhz) $\ldots$ .                                                                                   | 37  |

| 3.3 | Memory map for the wireless reader implementation on CC1010 $\ldots$ .                                                                               | 40  |

| 4.1 | $\mathbb{F}_{2^{163}}$ ECC software-only performance on an 8-bit AVR $\mu C~(@4~Mhz)~$ .                                                             | 46  |

| 4.2 | Software Only and Hardware Assisted Point Operation Performance (@4 $$                                                                               |     |

|     |                                                                                                                                                      | 54  |

| 4.3 | ECC Scalar Point Multiplication Performance (@4 Mhz)                                                                                                 | 55  |

| 5.1 | Format and description of useful instructions for OEF arithmetic                                                                                     | 62  |

| 6.1 | NIST recommended reduction polynomial for ECC and digit sizes possible                                                                               | 76  |

| 6.2 | LSD Multiplier: Latency and critical path                                                                                                            | 80  |

| 6.3 | Area and time complexity of $0.18 \mu m$ CMOS standard cells $\ldots$ $\ldots$                                                                       | 80  |

| 6.4 | LSD Multiplier: Area                                                                                                                                 | 85  |

| 7.1 | List of parameters suitable for optimized DFT modular multiplication.                                                                                | 92  |

| 7.2 | Equivalent Gate Count Area of ECC Processor                                                                                                          | .01 |

| 7.3 | Timing measurements (in clock cycles) for the ECC Processor 1                                                                                        | .02 |

| 7.4 | Controller Commands of ECC Processor                                                                                                                 | .03 |

| 7.5 | Point Doubling Instruction Sequence for ECC Processor                                                                                                | .04 |

| 7.6 | Point Addition Instruction Sequence for ECC Processor                                                                                                | .05 |

| 8.1 | Standards recommended field sizes for $\mathbb{F}_{2^m}$ and reduction polynomial $\ .$ | 107 |

|-----|-----------------------------------------------------------------------------------------|-----|

| 8.2 | $\mathbb{F}_{2^m}$ inversion cost using Itoh-Tsuji method                               | 110 |

| 8.3 | $\mathbb{F}_{2^m}$ Squaring unit requirements                                           | 117 |

| 8.4 | $\mathbb{F}_{2^m}$ ECC processor area (in equivalent gates)                             | 119 |

| 8.5 | $\mathbb{F}_{2^m}$ ECC processor performance @13.56 Mhz without extra register $R$ .    | 119 |

| 8.6 | $\mathbb{F}_{2^m}$ ECC processor performance @13.56 Mhz with extra register $R$         | 120 |

| 8.7 | Controller Commands of ECC Processor over $\mathbb{F}_{2^m}$                            | 121 |

# Chapter 1

# Introduction

Ubiquitous computing with low-cost pervasive devices have become a reality with sensor networks and RF-ID applications. Sensor networks offer tremendous benefits for the future as they have the potential to make life more convenient and safer. These constrained computing devices form large-scale collaborating networks by exchanging information. For instance, sensors can be used for climate control to reduce power consumption, for structures such as bridges to monitor the maintenance status, or for company badges to locate employees in order to increase productivity. Privacy and security of this information is important for the overall reliability of these networks and ultimately to the trustworthiness of the pervasive applications. Reliability in a lot of applications can be even more important than the secrecy of the data, because it is a protection against a failure by chance. In fact, security is often viewed as a crucial feature, a lack of which can be an obstacle to the wide-spread introduction of these applications. It is also important to note that a large share of those embedded applications will use wireless communication to reduce wiring costs, and increase flexibility and mobility. In addition, there is also a growing need for a rising number of modern appliances to be networked with each other, demanding solutions for cost-effective wireless networking. However, the main disadvantage of using a wireless network is that the communication channel is especially vulnerable to eavesdropping and the need for security becomes even more obvious.

Until a few years ago, only computers and data transferred through the Internet had been protected against unwanted harm. However, with the growing number of low-cost pervasive applications which are less secure than traditional systems, makes them an easy target for future attacks. This could include manipulating or preventing the functionality of these pervasive systems. In future, when more security critical applications begin to depend on such devices, functionality failures could be even lifethreatening.

We first present the security requirements in such systems (which are also equally applicable in general settings) and discuss the need for public key cryptography, in particular *Elliptic Curve Cryptography*.

# 1.1 Security Requirements and Techniques

Cryptography, or the art and science of keeping messages secure [70] involves mathematical techniques that provide the following security services:

- **Confidentiality** is a service used to keep the information accessible only to the authorized users of the communication. This service includes both protection of all user data transmitted between two points over a period of time as well as protection of traffic flow analysis.

- Integrity is a service that requires that system assets and transmitted information be capable of modification only by authorized users. Modification includes writing, changing the status, deleting, creating, delaying, and replaying of transmitted messages.

- Authentication is a service that is concerned with assuring that the origin of a message, date of origin, data content, time sent, etc are correctly identified. This service is subdivided into two major classes: entity authentication and data origin authentication. Note that the second class of authentication implicitly provides data integrity.

- **Non-repudiation** is a service which prevents both the sender and the receiver of a transmission from denying previous commitments or actions.

Symmetric-key cryptography (also known as private-key cryptography) provides the ability to securely and confidentially exchange messages between two parties. This is especially important if the data should not be revealed to any third party. Integrity can be guaranteed by using the proper *mode of operation* with the symmetric cipher. Authentication without non-repudiation can also be achieved using symmetric key cryptography if the secret key is known only to the two parties.

Some chip manufacturers have already understood these security needs and include small symmetric-key cryptographic co-processors for their low cost processors [13]. Though symmetric key algorithms do provide most of the security services, it has two major disadvantages:

- It requires secure transmission of a secret key, before being able to exchange messages.

- In a networked environment, each pair of users need a different key resulting in an *n* user system requiring  $\left(\frac{n \cdot (n-1)}{2}\right)$  key pairs .

Setting up this shared secret manually turns out to be unmanageable as such perversive applications involve a much larger number of entities than in traditional systems. It also introduces the problem of secure storage of the large number of secret key pairs.

Asymmetric-key cryptography (known generally as public-key (PK) cryptography) proposed in 1976 by Diffie and Hellman [18] introduces a new concept which can achieve the above security requirements including non-repudiation.

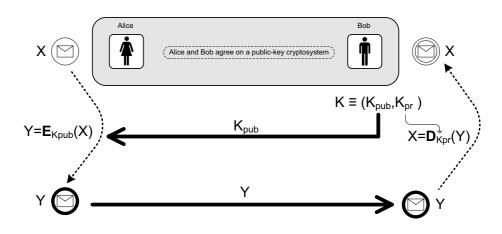

## 1.1.1 Public-Key Cryptography

Public-key cryptography is based on the idea of separating the key used to encrypt a message from the one used to decrypt it. Anyone who wants to send a message to a party, e.g., *Bob*, can encrypt that message using *Bob*'s *public key*, but only *Bob* can decrypt the message using his *private key*. The basic protocol between the two communication parties Alice and Bob can be seen in Figure 1.1, where  $K_{pub}$  denotes the public key of Bob and  $K_{pr}$  the private (not publicly available) key of Bob.

It is understood that the private key should be kept secret at all times and the public key is publicly available to everyone. Furthermore, it is computationally impossible (or in any reasonable amount of time) for anyone, except *Bob*, to derive the private key.

Public-key algorithm are not only used for the exchange of a key, but also for the authentication by using digital signatures. This enables the communication parties to prove that one of them had actually generated the message (non-repudiation). This is a crucial functionality to assure reliability in pervasive applications. It is important to note that sender non-repudiation can only be achieved using public-key cryptography.

One can realize three basic mechanisms with public–key algorithms:

- Key establishment protocols and key transport protocols without prior exchange of a joint secret,

- Digital signature algorithms, and

Figure 1.1: Public-key encryption protocol

■ Encryption.

Though public-key schemes can provide all functionality needed in modern security protocols such as SSL/TLS, it has been the hardest to implement due to its very high computational requirements. Even when properly implemented, all PK schemes proposed to date are several orders of magnitude slower than the best known private-key schemes. Hence, in practice, cryptographic systems are a mixture of symmetric-key and public-key cryptosystems and are called *hybrid cryptosystems*. A public-key algorithm is chosen for key establishment and then a symmetric-key algorithm is chosen to encrypt the communication data, achieving in this way high throughput rates.

In general, one can divide practical public-key algorithms into three families:

- Algorithms based on the Integer Factorization Problem (IFP): given a positive integer n, find its prime factorization. E.g., RSA [69], the most popular publickey algorithm named after its creators Rivest, Shamir, and Adelman

- Algorithms based on the *Discrete Logarithm Problem (DLP)*: given  $\alpha$  and  $\beta$  find positive integer k such that  $\beta = \alpha^k \mod p$ . E.g., the Diffie-Hellman (DH) key exchange protocol [18] and the Digital Signature Algorithm (DSA) [60].

- Algorithms based on *Elliptic Curve Discrete Logarithm Problem (ECDLP):* given points P and Q on an elliptic curve defined over a finite field, find positive integer k such that  $Q = k \cdot P$ . E.g., the *Elliptic Curve Diffie-Hellman* (ECDH) key exchange protocol and the *Elliptic Curve Digital Signature Algorithm* (ECDSA) [60].

In addition, there are many other public-key schemes, such as NTRU, or systems based on hidden field equations, which are not in wide spread use. The scientific community is only at the very beginning of understanding the security of such algorithms.

The computationally most intensive operation for RSA and Discrete Logarithm (DL) based public-key schemes are based on modular exponentiation, i.e., the operation  $x^e \mod n$ . These operations have to be performed using very long operands, typically 1024–2048 bits in length. However for ECDLP systems, the operands are in the range of 160–256 bits in length. An extended discussion regarding key equivalences between different asymmetric and symmetric cryptosystems in given in [51]. Table 1.1 puts the public–key bit length in perspective to the symmetric key algorithms.

| Symmetric-key | ECC     | RSA/DLP        | Remarks                               |  |

|---------------|---------|----------------|---------------------------------------|--|

| 64 bit        | 128 bit | 700 bit        | only short term security              |  |

|               |         |                | (breakable with some effort)          |  |

| 80 bit        | 160 bit | 1024 bit       | medium term security                  |  |

|               |         |                | (excl. government attacks)            |  |

| 128 bit       | 256 bit | 2048–3072 bits | long term security                    |  |

|               |         |                | (excl. advances in quantum computing) |  |

Table 1.1: Key length for public-key and symmetric-key cryptography

## 1.1.2 Elliptic Curve Cryptography (ECC)

*Elliptic Curve Cryptography* is a relatively new cryptosystem, suggested independently in 1986 by Miller [55] and Koblitz [43]. At present, ECC has been commercially accepted, and has also been adopted by many standardizing bodies such as ANSI [2], IEEE [36], ISO [38] and NIST [60].

Elliptic curve cryptosystems are based on the well known Discrete Logarithm Problem (DLP). Elliptic curves defined over a finite field provide a group structure that is used to implement the cryptographic schemes. The elements of the group are the rational points on the elliptic curve, together with a special point  $\mathcal{O}$  (called the "point at infinity") acting as the identity element of the group. The group operation is the addition of points, which can be carried out by means of arithmetic operations in the underlying finite field (which will be discussed in detail in Chapter 2). A major building block of all elliptic curve cryptosystems is the *scalar point multiplication*, an operation of the form  $k \cdot P$  where k is a positive integer and P is a point on the elliptic curve. Computing  $k \cdot P$  means adding the point P exactly k - 1 times to itself, which results in another point Q on the elliptic curve<sup>1</sup>. The inverse operation, i.e., to recover k when the points P and  $Q = k \cdot P$  are given, is known as the *Elliptic Curve Discrete Logarithm Problem* (ECDLP). To date, no subexponential-time algorithm is known to solve the ECDLP in a properly selected elliptic curve group [61]. This makes *Elliptic Curve Cryptography* a promising branch of public key cryptography which offers similar security to other "traditional" DLP-based schemes in use today, with smaller key sizes and memory requirements, e.g., 160 bits instead of 1024 bits (as shown in Table 1.1).

Many of the new security protocols decouple the choice of cryptographic algorithm from the design of the protocol. Users of the protocol negotiate on the choice of algorithm to use for a particular secure session. Hence, ECC based algorithms can be easily integrated into existing protocols to achieve the same security and backward compatibility with smaller resources. Hence more low-end constrained devices can use such protocols which till recently were considered unsuitable for such systems.

# 1.2 Thesis Outline

With *Elliptic Curve Cryptography* emerging as a serious alternative, the desired level of security can be attained with significantly smaller keys. This makes ECC very attractive for small-footprint devices with limited computational capacities, memory and low-bandwidth network connections. Another major advantage of ECC is that the domain parameters can be (judiciously) chosen to improve implementation performance. However ECC is still considered to be impracticable for very low-end devices. In this thesis, we show that *Elliptic Curve Cryptography* can indeed be used on such constrained devices without adversely affecting performance. This is made possible based on the flexibility that ECC provides in terms of the choice of different algorithms and parameters. We present techniques for ECC implementation in three domains: pure software based implementations on low-end processors, hardware/software co-design with extensions for such processors, and finally stand alone low area cryptographic processors.

In Chapter 2, we first present the mathematical background to the elliptic curves over different finite fields and their group operations. We also present the different algorithms that are used for the implementation of the finite field arithmetic and the

<sup>&</sup>lt;sup>1</sup>Scalar multiplication in an additive group is the equivalent operation to exponentiation in a multiplicative group.

point arithmetic. We restrict our attention only to those algorithms that are relevant to this thesis. The two most common schemes, ECDH and ECDSA are also presented.

In Chapter 3, we present a public-key cryptographic implementation for secure key exchange on low-end wireless devices used in sensor networks using elliptic curves. Our implementation is based on *Optimal Extension Fields* (OEF) that are a special type of finite fields  $\mathbb{F}_{p^m}$ . As our platform we chose a Chipcon CC1010 chip [13] which is based on the 8051 architecture and is especially suited for secure wireless applications as it has a built-in radio transceiver as well as a hardware DES engine. We were able to establish a secure end-to-end connection between the sensor and a base station in an acceptable time of 3 seconds without requiring a cryptographic coprocessor.

In Chapter 4, we describes a proof-of-concept implementation for an extremely lowcost instruction set extension using reconfigurable logic, which enables an 8-bit AVR micro-controller running at 4 Mhz (a typical representative for a low-cost pervasive processor) to provide full size elliptic curve cryptographic capabilities. We show that a standard compliant 163-bit point multiplication can be computed in 0.113 sec on an 8-bit AVR micro-controller running at 4 Mhz with minimal extra hardware. Our design not only accelerates the computation by a factor of more than 30 compared to a software-only solution, it also reduces the code-size and data-RAM.

In Chapter 5, we investigate the potential of architectural enhancements and instruction set extensions for low-level arithmetic used in public-key cryptography, most notably multiplication in finite fields of large order. The focus of the contribution is directed towards the special Optimal Extension Fields where p is a pseudo-Mersenne (PM) prime of the form  $p = 2^n - c$  that fits into a single register. Based on the MIPS32 instruction set architecture, we introduce two custom instructions to accelerate the reduction modulo a PM prime. Moreover, we show that the multiplication in an OEF can take advantage of a multiply and accumulate unit with a wide accumulator, so that a certain number of 64-bit products can be summed up without overflow. The proposed extensions support a wide range of PM primes and allow a reduction modulo  $2^n - c$  to complete in only four clock cycles when  $n \leq 32$ .

In Chapter 6, we show different architectural enhancements in Least Significant Digit (LSD) multiplier for binary fields  $\mathbb{F}_{2^m}$ . Digit Serial Multipliers are now used extensively in hardware implementations of *Elliptic Curve Cryptography*. We propose two new different architectures, the Double Accumulator Multiplier (DAM) and N-Accumulator Multiplier (NAM) which are both faster compared to traditional LSD multipliers. Our evaluation of the multipliers for different digit sizes gives optimum choices and shows that presently used digit sizes are the worst possible choices. Hence, one of the most important results of this contribution is that digit sizes of the form  $2^{l} - 1$ , where l is an integer, are preferable for the digit multipliers. Furthermore, we show that one should always use the NAM architecture to get the best timings. Considering the time area product DAM or NAM gives the best performance depending on the digit size.

In Chapter 7, we propose an area/time efficient ECC processor architecture which performs all finite field arithmetic operations in the discrete Fourier domain. The proposed architecture utilizes a class of OEF  $\mathbb{F}_{p^m}$  where the field characteristic is a Mersenne prime  $p = 2^n - 1$  and m = n. The main advantage of our architecture is that it achieves extension field modular multiplication in the *discrete Fourier domain* with only a *linear* number of base field  $\mathbb{F}_p$  multiplications in addition to quadratic number of simpler operations such as addition and bitwise rotation. With its low area and high speed, the proposed architecture is well suited for *Elliptic Curve Cryptography* in constrained environments such as wireless sensor networks.

In Chapter 8, we present a stand-alone highly area optimized ECC processor design for standards compliant binary field curves. We use the fast squarer implementation to construct an addition chain that allows inversion to be computed efficiently. Hence, we propose an affine co-ordinate ASIC implementation of the ECC processor using a modified Montgomery point multiplication method for binary curves ranging from 133 - 193 bits. An area between 10k and 18k gates on a 0.35um CMOS process is possible for the different curves which makes the design very attractive for enabling ECC in constrained devices.

We finally end this dissertation with a summary of our work and some suggestions for future research.

# **Chapter 2**

# **Mathematical Background**

Parts of this chapter are published in the survey articles [28] and [27]

# 2.1 Introduction to Elliptic Curves

An elliptic curve E over a field K is the set of solutions to the cubic equation

$$E: F(x,y) = y^{2} + a_{1}xy + a_{3}y - x^{3} - a_{2}x^{2} - a_{4}x - a_{6} = 0 \text{ where } a_{i} \in K.$$

and the discriminant defined as

$$\Delta = -d_2^2 d_8 - 8d_4^3 - 27d_6^2 + 9d_2d_4d_6 \neq 0$$

where

$$d_2 = a_1^2 + 4a_2$$

$$d_4 = 2a_4 + a_1a_3$$

$$d_6 = a_3^2 + 4a_6$$

$$d_8 = a_1^2a_6 + 4a_2a_6 - a_1a_3a_4 + a_2a_3^2 - a_4^2.$$

If L is an extension field of K, then the set of *L*-rational points on E is given as

$$E(L) = \{(x, y) \in L \times L : F(x, y) = 0\} \cup \{\mathcal{O}\}$$

(2.1)

where  $\mathcal{O}$  is the point at infinity.

We construct an additive abelian group (E, +) given by the points on the curve and an additive group operation defined on these points. Hence, **Set** E: Points on the curve given by E(L).

• **Operation** +:  $P + Q = (x_1, y_1) + (x_2, y_2) = R = (x_3, y_3).$

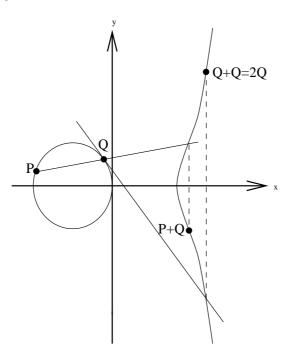

Figure 2.1 shows an example of an elliptic curve over the field of real numbers. Finding P + Q = R in a geometrical manner can be achieved by the following two steps and is shown in Figure 2.1:

- a)  $P \neq Q \rightarrow$  line through P and Q and mirror the point of third interception along the x-axis.

- b)  $P = Q \Rightarrow P + Q = 2Q \rightarrow$  tangent line through Q and mirror the point of second intersection along the x-axis.

Figure 2.1:  $y^2 = x^3 + a \cdot x + b$  over the reals

A more detailed discussion on elliptic curves can be found in [75].

# 2.2 Elliptic Curve Parameter Selection

An implementation of an elliptic curve cryptosystem requires a number of decisions to be taken at different *hierarchy* levels depending on the underlying hardware and implementation goals that need to be achieved.

#### ■ At the field level

- $\square$  Selection of the underlying field (could be  $\mathbb{F}_{2^m}$ ,  $\mathbb{F}_p$  or  $\mathbb{F}_{p^m}$ ).

- $\Box$  Choosing the field representation (e.g., polynomial basis or normal basis).

- □ Field arithmetic algorithms for field addition (subtraction), multiplication, reduction and inverse.

#### ■ At the elliptic curve level

- $\Box$  Choosing the type of representation for the points (affine or projective coordinates).

- $\Box$  Choosing a point addition and doubling algorithm.

#### ■ At the protocol level

- $\Box$  Choosing the appropriate protocol (key-exchange or signature).

- $\Box$  Choosing the algorithm for scalar multiplication  $k \cdot P$ .

These choices provide a huge flexibility and hence makes ECC viable for both constrained devices and high performance servers. We first present the arithmetic for different elliptic curves defined over three different field choices  $\mathbb{F}_p$  (Section 2.3),  $\mathbb{F}_{2^m}$ (Section 2.4) and  $\mathbb{F}_{p^m}$  (Section 2.5). Then we present the different methods to perform the point multiplication in Section 2.6. In Section 2.7, the key-exchange and signature protocols are discussed. The algorithms that are presented here are limited only to those that are relevant to this thesis. A more exhaustive list of different algorithms can be found in references [34, 54].

# **2.3** Elliptic Curve Arithmetic over $\mathbb{F}_p$

An elliptic curve E over  $\mathbb{F}_p$  (*characteristic* not equal to 2 or 3) is the set of solutions (x, y) which satisfy the simplified Weierstrass equation:

$$E: y^2 = x^3 + ax + b (2.2)$$

where  $a, b \in \mathbb{F}_p$  and  $4a^3 + 27b^2 \neq 0$ , together with the point at infinity  $\mathcal{O}$ . The group laws are defined in terms of underlying field operations in  $\mathbb{F}_p$  as follows:

#### Identity

$P + \mathcal{O} = \mathcal{O} + P = P$  for all  $P \in E(\mathbb{F}_p)$ .

#### Negation

If  $P = (x, y) \in E(\mathbb{F}_p)$ , then  $P + Q = \mathcal{O}$  is given by the point  $Q = (x, -y) \in E(\mathbb{F}_p)$ which is the negation of P (denoted as -P). Note,  $-\mathcal{O} = \mathcal{O}$ .

#### **Point Addition and Doubling**

Let  $P = (x_0, y_0) \in E(\mathbb{F}_p)$  and  $Q = (x_1, y_1) \in E(\mathbb{F}_p)$ , where  $Q \neq -P$ . Then  $P + Q = (x_2, y_2)$ , where

$$\begin{aligned} x_2 &= \lambda^2 - x_0 - x_1 \\ y_2 &= \lambda(x_1 - x_2) - y_1 \end{aligned}$$

(2.3)

and

$$\lambda = \begin{cases} \frac{y_0 - y_1}{x_0 - x_1} & \text{if } P \neq Q \\ \\ \frac{3x_1^2 + a}{2y_1} & \text{if } P = Q \end{cases}$$

#### Projective coordinate representations

The coordinate representation considered so far is known as the affine representation. However, in many applications it is more convenient to represent the points P and Q in projective coordinates.

- In the standard projective coordinates, a point is represented by the tuple  $(X : Y : Z), Z \neq 0$  which corresponds to the affine point (X/Z, Y/Z). The point at infinity  $\mathcal{O}$  is (0:1:0) and the negative of (X : Y : Z) is (X : -Y : Z).

- In the Jacobian projective coordinates, a point is similarly represented by the tuple  $(X : Y : Z), Z \neq 0$  which corresponds to the affine point  $(X/Z^2, Y/Z^3)$ . The point at infinity  $\mathcal{O}$  is (1 : 1 : 0) and the negative of (X : Y : Z) is (X : -Y : Z).

This representation is advantageous when inversion is computationally much more expensive compared to multiplication in the finite field. The algorithms for projective coordinates trade inversions in the point addition and doubling operations for a larger number of multiplications followed by single inversion at the end of the algorithm. This single inversion can be computed via exponentiation using the *Fermat's Little* Theorem [12]:  $x^{-1} \equiv x^{p-2} \mod p$ .

One can derive expressions equivalent to Eq. 2.3 for point addition and doubling operations in both the projective coordinates. We refer to [34] for the actual algorithms. In Table 2.1 we present the complexity of the group operations considering different coordinates representations. The complexity of addition or doubling a point on an elliptic curve is given by the number of field multiplications, squarings and inversions (if affine coordinates are being used). Field additions are relatively cheap operations compared to multiplications or inversions, and therefore are neglected in the tables.

Table 2.1: Operation counts for point addition and doubling on  $y^2 = x^3 - 3x + b$ . A = affine, P = standard projective, J = Jacobin, I = field inversion, M = field multiplication, S = field squaring [34]

| Doubling           |            | General addition      |            | Mixed coordinates |        |

|--------------------|------------|-----------------------|------------|-------------------|--------|

| $\boxed{2A \to A}$ | 1I, 2M, 2S | $A + A \to A$         | 1I, 2M, 1S | $J + A \to J$     | 8M, 3S |

| $2P \rightarrow P$ | 7M, 3S     | $P + P \rightarrow P$ | 12M, 2S    |                   |        |

| $2J \rightarrow J$ | 4M, 4S     | $J + J \rightarrow J$ | 12M, 4S    |                   |        |

# 2.3.1 Field Arithmetic over $\mathbb{F}_p$

To perform the above introduced group operations, we have to compute the underlying field arithmetic operations on the prime field. The crucial field operations are the modular addition, subtraction, multiplication and inverse.

## **Addition and Subtraction**

Field addition over  $\mathbb{F}_p$  is performed using multi-precision integer addition followed by a reduction if required as shown in Algorithm 2.1.

Algorithm 2.1 Addition in  $\mathbb{F}_p$

Input:  $A, B \in \mathbb{F}_p$ . Output:  $C \equiv A + B \mod p$ . 1:  $C \leftarrow A + B$  {multi-precision integer addition} 2: if  $C \ge p$  then 3:  $C \leftarrow C - p$ 4: end if 5: Return (C)

Similarly subtraction in  $\mathbb{F}_p$  is a multi-precision integer subtraction followed by an additional addition with p if the result is negative (Algorithm 2.2).

Algorithm 2.2 Subtraction in  $\mathbb{F}_p$ Input:  $A, B \in \mathbb{F}_p$ . Output:  $C \equiv A - B \mod p$ . 1:  $C \leftarrow A - B$  {multi-precision integer subtraction} 2: if C < 0 then 3:  $C \leftarrow C + p$ 4: end if 5: Return (C)

## **Multiplication and Squaring**

Modular multiplication or squaring can be done by first performing a multi-precision integer multiplication or squaring, respectively, and then reducing the double bit-length result with the prime p. Multi-precision integer multiplication and squaring can be done based on different techniques like operand scanning, product scanning [15] or Karatsuba method [41]. Each of them has its advantages and disadvantages based on the underlying implementation hardware.

### **Field Reduction**

Field reduction can be performed very efficiently if the modulus p is a generalized Mersenne (GM) prime. These primes are sum or differences of a small number of powers of 2 and have been adopted as recommended curves in different standards like NIST [60], ANSI [2] and SEC [1]. The normally used GM primes for different field sizes are shown here:

$$p_{160} = 2^{160} - 2^{31} - 1$$

$$p_{192} = 2^{192} - 2^{64} - 1$$

$$p_{256} = 2^{256} - 2^{224} + 2^{192} + 2^{96} - 1$$

Fast reduction is possible using these primes since the powers of 2 translate naturally to bit locations in hardware. For e.g.,  $2^{160} \equiv 2^{31} + 1 \mod p_{160}$  and therefore each of the higher bits can be wrapped to the lower bit locations based on the equivalence. The steps required to compute the fast reduction using GM primes is given in NIST [60]

However when using general primes which are not GM primes, two other different techniques can be used: Barrett reduction and Montgomery reduction.

The Barrett reduction [8] for  $r = x \mod p$  is shown in Algorithm 2.3. It requires a precomputation of  $\mu = \lfloor b^{2k}/p \rfloor$  where b is the radix for the representation of x and is mostly chosen to be the word-size of the processor. This allows all divisions to be performed in the algorithm as simple word level shifts. The method is suitable if many reductions are to be done using the same modulus, which is mostly the case.

Algorithm 2.3 Barrett reduction in  $\mathbb{F}_p$ Input:  $x \leq b^{2k}$  where  $b \geq 3$ , and  $\mu = \lfloor b^{2k}/p \rfloor$  where  $k = \lfloor \log_b p \rfloor + 1$ . Output:  $r \equiv x \mod p$ . 1:  $\hat{q} \leftarrow \lfloor \lfloor x/b^{k-1} \rfloor \cdot \mu/b^{k+1} \rfloor$ . 2:  $r \leftarrow (z \mod b^{k+1}) - (\hat{q} \cdot p \mod b^{k+1})$ . 3: If r < 0 then  $r \leftarrow r + b^{k+1}$ . 4: While  $r \geq p$  do:  $r \leftarrow r - p$ . 5: Return (r)

The Montgomery method [58] uses a special representation to perform arithmetic efficiently. The cost for changing the representation is costly and therefore this method is useful only if performing multiple reductions using the same modulus. Let R > pwith gcd(R,p) = 1, then the Montgomery reduction of x < pR is  $r = xR^{-1} \mod p$ . The Algorithm 2.4 shows the procedure where the elements are represented in word basis b. Choosing  $R = b^n$  allows the different operations to be simple word level shifts.

Algorithm 2.4 Montgomery reduction in  $\mathbb{F}_p$

Input: x < pR where  $R = b^n$ , gcd(p, b) = 1, and  $p' = -p^{-1} \mod b$ . Output:  $r \equiv xR^{-1} \mod p$ . 1:  $r \leftarrow x$  {Notation:  $(r_{2n-1} \cdots r_1 r_0)$ } 2: for *i* from 0 to (n-1) do 3:  $u_i \leftarrow r_i p' \mod b$ . 4:  $r \leftarrow r + u_i p \ b^i$ . 5: end for 6:  $r \leftarrow r/b^n$ 7: If  $r \ge p$  then  $r \leftarrow r - p$ . 8: Return (r).

#### Inversion

Inversion is performed using extended binary Euclidean algorithm which replaces the expensive division with shifts as shown in Algorithm 2.5.

Algorithm 2.5 Binary Euclidean algorithm in  $\mathbb{F}_p$

```

Input: Prime p and x \in [1, p).

Output: r \equiv x^{-1} \mod p.

1: u \leftarrow x, v \leftarrow p.

2: x_1 \leftarrow 1, x_2 \leftarrow 0.

3: while u \neq 1 and v \neq 1 do

while u is even do

4:

u \leftarrow u/2.

5:

If x_1 is even then x_1 \leftarrow x_1/2; else x_1 \leftarrow (x_1 + p)/2.

6:

end while

7:

while v is even do

8:

v \leftarrow v/2.

9:

If x_2 is even then x_2 \leftarrow x_2/2; else x_2 \leftarrow (x_2 + p)/2.

10:

end while

11:

12:

If u \ge v then u \leftarrow u - v, x_1 \leftarrow x_1 - x_2;

Else v \leftarrow v - u, x_2 \leftarrow x_2 - x_1.

13:

14: end while

15: If u = 1 then Return (x_1 \mod p); else Return (x_2 \mod p).

```

# **2.4** Elliptic Curve Arithmetic over $\mathbb{F}_{2^m}$

An elliptic curve E over  $\mathbb{F}_{2^m}$  is the set of solutions (x, y) which satisfy the simplified Weierstrass equation:

$$E: y^2 + xy = x^3 + ax^2 + b \tag{2.4}$$

where  $a, b \in \mathbb{F}_{2^m}$  and  $b \neq 0$ , together with the point at infinity  $\mathcal{O}$ . Due to the Weil Descent attack [21], m is chosen to be a prime.

The group laws are defined in terms of underlying field operations in  $\mathbb{F}_{2^m}$  as follows:

#### Identity

$P + \mathcal{O} = \mathcal{O} + P = P$  for all  $P \in E(\mathbb{F}_{2^m})$ .

#### Negation

If  $P = (x, y) \in E(\mathbb{F}_{2^m})$ , then  $P + Q = \mathcal{O}$  is given by the point  $Q = (x, x + y) \in E(\mathbb{F}_{2^m})$ which is the negation of P (denoted as -P). Note,  $-\mathcal{O} = \mathcal{O}$ .

#### **Point Addition and Doubling**

Let  $P = (x_0, y_0) \in E(\mathbb{F}_{2^m})$  and  $Q = (x_1, y_1) \in E(\mathbb{F}_{2^m})$ , where  $Q \neq -P$ . Then  $P + Q = (x_2, y_2)$ , where

$$\begin{aligned} x_2 &= \lambda^2 + \lambda + x_0 + x_1 + a \\ y_2 &= \lambda(x_0 + x_2) + x_2 + y_0 \end{aligned}$$

(2.5)

and

$$\lambda = \begin{cases} \frac{y_0 + y_1}{x_0 + x_1} & \text{if } P \neq Q \\ \\ x_1 + \frac{y_1}{x_1} & \text{if } P = Q \end{cases}$$

#### **Projective coordinate representations**

It is more convenient to represent the points P and Q in projective coordinates when inversions are computationally more expensive compared to multiplications in  $\mathbb{F}_{2^m}$ .

In the standard projective coordinates, a point is represented by the tuple  $(X : Y : Z), Z \neq 0$  which corresponds to the affine point (X/Z, Y/Z). The point at infinity  $\mathcal{O}$  is (0:1:0) and the negative of (X : Y : Z) is (X : X + Y : Z).

- In the Jacobian projective coordinates, a point is represented by the tuple  $(X : Y : Z), Z \neq 0$  which corresponds to the affine point  $(X/Z^2, Y/Z^3)$ . The point at infinity  $\mathcal{O}$  is (1:1:0) and the negative of (X : Y : Z) is (X : X + Y : Z).

- In the López-Dahab (LD) coordinates, a point is represented by the tuple  $(X : Y : Z), Z \neq 0$  which corresponds to the affine point  $(X/Z, Y/Z^2)$ . The point at infinity  $\mathcal{O}$  is (1:0:0) and the negative of (X : Y : Z) is (X : X + Y : Z).

We refer to [34] for expressions equivalent to Eq. 2.5 for the point addition and doubling operations in the projective coordinates. In Table 2.2, we present the complexity of the group operations considering different coordinates representations.

Table 2.2: Operation counts for point addition and doubling on  $y^2 + xy = x^3 + ax^2 + b$ . M =field multiplication, D =field division [34]

| Coordinate system      | General addition | Mixed coordinates | Doubling |

|------------------------|------------------|-------------------|----------|

| Affine                 | D + M            |                   | D + M    |

| Standard projective    | 13M              | 12M               | 7M       |

| Jacobian projective    | 14M              | 8M                | 4M       |

| López-Dahab projective | 14M              | 8M                | 4M       |

## **2.4.1** Field Arithmetic over $\mathbb{F}_{2^m}$

The field operations required to implement the elliptic curve group operation are addition, multiplication (squaring) and inverse in  $\mathbb{F}_{2^m}$ .

## **Polynomial Basis Representation**

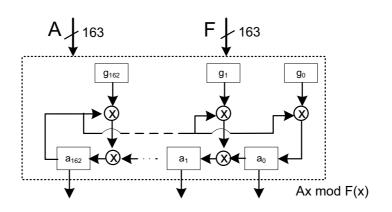

The standard polynomial basis representation is used for our implementations with the reduction polynomial  $F(x) = x^m + G(x) = x^m + \sum_{i=0}^{m-1} g_i x^i$  where  $g_i \in \{0, 1\}$ , for i = 1, ..., m-1 and  $g_0 = 1$ .

Let  $\alpha$  be a root of F(x), then we represent  $A \in \mathbb{F}_{2^m}$  in polynomial basis as

$$A(\alpha) = \sum_{i=0}^{m-1} a_i \alpha^i, \ a_i \in \mathbb{F}_2$$

(2.6)

This polynomial can also be represented as a bit vector:  $(a_{m-1}, ..., a_1, a_0)$ .

The field arithmetic is implemented as polynomial arithmetic modulo F(x). Notice that by assumption  $F(\alpha) = 0$  since  $\alpha$  is a root of F(x). Therefore,

$$\alpha^m = -G(\alpha) = \sum_{i=0}^{m-1} g_i \alpha^i$$

(2.7)

gives an easy way to perform modulo reduction whenever we encounter powers of  $\alpha$  greater than m-1. Throughout the text, we will write  $A \mod F(\alpha)$  to mean *explicitly* the reduction step.

#### Addition

$\mathbb{F}_{2^m}$  addition is the simplest of all operations, since it is a bitwise addition in  $\mathbb{F}_2$  which maps to an XOR operation  $(\oplus)$  in software or hardware.

$$C \equiv A + B \mod F(\alpha)$$

$$\equiv (a_{m-1} \oplus b_{m-1})\alpha^{m-1} + \ldots + (a_1 \oplus b_1)\alpha + (a_0 \oplus b_0)$$

#### **Multiplication and Squaring**

The multiplication of two elements  $A, B \in \mathbb{F}_{2^m}$ , with  $A(\alpha) = \sum_{i=0}^{m-1} a_i \alpha^i$  and  $B(\alpha) = \sum_{i=0}^{m-1} b_i \alpha^i$  is given as

$$C(\alpha) = \sum_{i=0}^{m-1} c_i \alpha^i \equiv A(\alpha) \cdot B(\alpha) \mod F(\alpha)$$

(2.8)

where the multiplication is a polynomial multiplication, and all  $\alpha^t$ , with  $t \ge m$  are reduced with Eq. 2.7.

The simplest algorithm for field multiplication is the shift-and-add method [42] with the reduction step inter-leaved (Algorithm 2.6). The shift-and-add method is not suitable for software implementations as the bitwise shifts are hard to implement across the words on a processor. A more efficient method for implementing the multiplier in software is the Comb method [53]. Here the multiplication is implemented efficiently in two separate steps, first performing the polynomial multiplication to obtain 2n-bit length polynomial and then reducing it using special reduction polynomials.

Algorithm 2.7 shows the polynomial multiplication using the Comb method. The operation SHIFT  $(A \ll k) = \sum_{i=0}^{m-1} a_i \alpha^{(i+k)}$ , performs a k-bit shift across the words

Algorithm 2.6 Shift-and-Add Most Significant Bit (MSB) first  $\mathbb{F}_{2^m}$  multiplication

**Input:**  $A = \sum_{i=0}^{m-1} a_i \alpha^i$ ,  $B = \sum_{i=0}^{m-1} b_i \alpha^i$  where  $a_i, b_i \in \mathbb{F}_2$ . **Output:**  $C \equiv A \cdot B \mod F(\alpha) = \sum_{i=0}^{m-1} c_i \alpha^i$  where  $c_i \in \mathbb{F}_2$ . 1:  $C \leftarrow 0$ 2: **for** i = m - 1 downto 0 **do** 3:  $C \leftarrow b_i \cdot (\sum_{i=0}^{m-1} a_i \alpha^i) + (\sum_{i=0}^{m-1} c_i \alpha^i) \cdot \alpha \mod F(\alpha)$ 4: **end for** 5: Return (C)

**Algorithm 2.7** Comb Method for  $\mathbb{F}_{2^m}$  multiplication on a *w*-bit processor.

Input:  $A = \sum_{i=0}^{m-1} a_i \alpha^i$ ,  $B = \sum_{i=0}^{m-1} b_i \alpha^i$  where  $a_i, b_i \in \mathbb{F}_2$  and  $s = \lceil \frac{m}{w} \rceil$ . Output:  $C = A \cdot B = \sum_{i=0}^{2m-1} c_i \alpha^i$ , where  $c_i \in \mathbb{F}_2$ 1:  $C \leftarrow 0$ 2: for j = 0 to w - 1 do 3: for i = 0 to s - 1 do 4:  $C \leftarrow b_{wi+j} \cdot \text{SHIFT}(A << w.i) + C$ 5: end for 6:  $A \leftarrow \text{SHIFT}(A << 1)$ 7: end for 8: Return (C)

without reduction. It is important to note that  $\text{SHIFT}(A \ll w.i)$  where w is the wordlength of the processor, are the same original set of bytes referenced with a different memory pointer and therefore requires no actual shifts in software.

For hardware, the shift-and-add method can be implemented efficiently and is suitable when area is constrained. When the bits of B are processed from the mostsignificant bit to the least-significant bit (as in Algorithm 2.6), then its implemented as Most-Significant Bit-serial (MSB) multiplier. Similarly a Least-Significant Bit-serial (LSB) multiplier can be implemented and the choice between the two depends on the design architecture and goals. Digit multipliers, introduced in [76], are a trade-off between speed, area, and power consumption. This is achieved by processing several of B's coefficients at the same time. The number of coefficients that are processed in parallel is defined to be the digit-size D.

The total number of digits in the polynomial of degree m-1 is given by  $d = \lfloor m/D \rfloor$ .

Then, we can re-write the multiplier as  $B = \sum_{i=0}^{d-1} B_i \alpha^{D_i}$ , where

$$B_i = \sum_{j=0}^{D-1} b_{Di+j} \alpha^j \quad 0 \le i \le d-1$$

(2.9)

and we assume that B has been padded with zero coefficients such that  $b_i = 0$  for  $m - 1 < i < d \cdot D$  (i.e., the size of B is  $d \cdot D$  coefficients, but  $\deg(B) < m$ ). The multiplication can then be performed as:

$$C \equiv A \cdot B \mod p(\alpha) = A \cdot \sum_{i=0}^{d-1} B_i \alpha^{D_i} \mod p(\alpha)$$

(2.10)

The Least-Significant Digit-serial (LSD) multiplier is a generalization of the LSB multiplier in which the digits of B are processed starting from the least significant to the most significant. Using Eq. 2.10, the product in this scheme can be represented as follows

$$C \equiv A \cdot B \mod p(\alpha)$$

$$\equiv [B_0 A + B_1(A\alpha^D \mod p(\alpha)) + B_2(A\alpha^D \alpha^D \mod p(\alpha)) + \dots + B_{d-1}(A\alpha^{D(d-2)}\alpha^D \mod p(\alpha))] \mod p(\alpha)$$

Algorithm 2.8 shows the details of the LSD Multiplier.

Algorithm 2.8 Least Significant Digit-serial (LSD) Multiplier [76] Input:  $A = \sum_{i=0}^{m-1} a_i \alpha^i$ , where  $a_i \in \mathbb{F}_2$ ,  $B = \sum_{i=0}^{\lceil \frac{D}{D} \rceil - 1} B_i \alpha^{Di}$ , where  $B_i$  is as in (2.9) Output:  $: C \equiv A \cdot B = \sum_{i=0}^{m-1} c_i \alpha^i$ , where  $c_i \in \mathbb{F}_2$ 1:  $C \leftarrow 0$ 2: for i = 0 to  $\lceil \frac{m}{D} \rceil - 1$  do 3:  $C \leftarrow B_i A + C$ 4:  $A \leftarrow A \alpha^D \mod p(\alpha)$ 5: end for 6: Return  $(C \mod p(\alpha))$

**Remark.** If C is initialized to value  $I \in \mathbb{F}_{2^m}$  in Algorithm 2.8, then we can obtain as output the quantity,  $A \cdot B + I \mod p(\alpha)$  at no additional (hardware or delay) cost. This operation, known as a multiply/accumulate operation is very useful in elliptic curve based systems.

Field squaring is much simpler in  $\mathbb{F}_{2^m}$  when represented in polynomial basis as show here:

$$C \equiv A^{2} \mod F(\alpha) \equiv (a_{m-1}\alpha^{2(m-1)} + a_{m-2}\alpha^{2(m-2)} + \ldots + a_{1}\alpha^{2} + a_{0}) \mod F(\alpha)$$

(2.11)

Polynomial squaring is implemented by expanding C to double its bit-length by interleaving 0 bits in between the original bits of C and then reducing the double length result.

#### **Field Reduction**

Field reduction of a 2*n*-bit size polynomial in  $\mathbb{F}_{2^m}$  can be efficiently performed if the reduction polynomial F(x) is a trinomial or pentanomial, i.e.,

$$F(x) = x^m + x^k + 1$$

or

$$F(x) = x^m + x^j + x^k + x^l + 1$$

Such polynomials are widely recommended in all the major standards [2, 36, 60]. For software implementation, reduction polynomials with the middle terms close to each other are more suitable while for hardware, polynomials with a smaller second highest degree are favorable. The implementation techniques using the different reduction polynomials can be found in [11].